#### **III Semester**

| ANAI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OG AND DIGITAL                                                                                                                                                                                                                                                                                                                                                                                                   | ELECTRONICS                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Course Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21CS33                                                                                                                                                                                                                                                                                                                                                                                                           | CIE Marks                                                                                                                                                                                                                                                                                                             | 50                                                                                                                                                                                               |

| Teaching Hours/Week (L:T:P: S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3:0:2:0                                                                                                                                                                                                                                                                                                                                                                                                          | SEE Marks                                                                                                                                                                                                                                                                                                             | 50                                                                                                                                                                                               |

| Total Hours of Pedagogy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40 T + 20 P                                                                                                                                                                                                                                                                                                                                                                                                      | Total Marks                                                                                                                                                                                                                                                                                                           | 100                                                                                                                                                                                              |

| Credits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 04                                                                                                                                                                                                                                                                                                                                                                                                               | Exam Hours                                                                                                                                                                                                                                                                                                            | 03                                                                                                                                                                                               |

| Credits Course Learning Objectives: CLO 1. Explain the use of photo electives: CLO 2. Make use of simplifying tech CLO 3. Illustrate combinational and CLO 4. Demonstrate the use of flipf CLO 5. Design and test counters, An Teaching-Learning Process (Geneent These are sample Strategies, which to outcomes. 1. Lecturer method (L) does nate teaching methods may be acceded and the second of the s | ctronics devices, 555<br>aniques in the design<br>sequential digital ci-<br>lops and apply for re-<br>nalog-to-Digital and l<br><b>ral Instructions)</b><br>eachers can use to a<br>ot mean only tradition<br>dopted to develop th<br>s to explain function<br>roup Learning) Learn<br>ner order Thinking) of<br>hing (PBL), which fos<br>pility to evaluate, gen<br>a multiple represen<br>solve the same probl | timer IC, Regulator ICs<br>of combinational circui<br>rcuits<br>egisters<br>Digital-to-Analog conver<br>ccelerate the attainment<br>onal lecture method, but<br>e outcomes.<br>ing of various concepts.<br>ning in the class.<br>questions in the class, w<br>sters students' Analytica<br>heralize, and analyze info | and uA741<br>its.<br>rsion techniques.<br>c of the various course<br>different type of<br>hich promotes critical<br>l skills, develop<br>ormation rather than                                    |

| 8. Discuss how every concept improve the students' unde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                  | e real world - and when t                                                                                                                                                                                                                                                                                             | hat's possible, it helps                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Module-1                                                                                                                                                                                                                                                                                                                                                                                                         | l                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                  |

| BJT Biasing: Fixed bias, Collector to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | oase Bias, voltage div                                                                                                                                                                                                                                                                                                                                                                                           | vider bias                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                  |

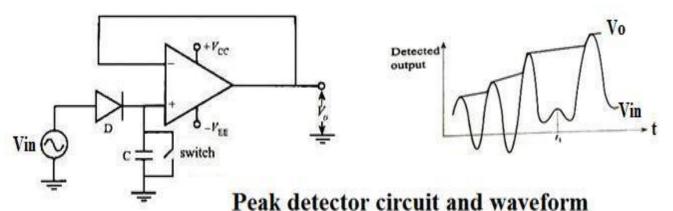

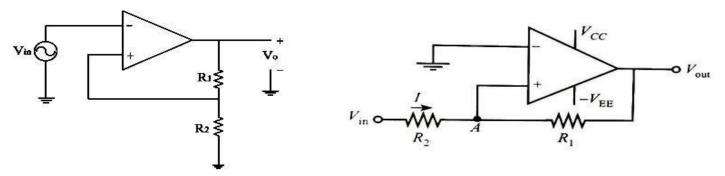

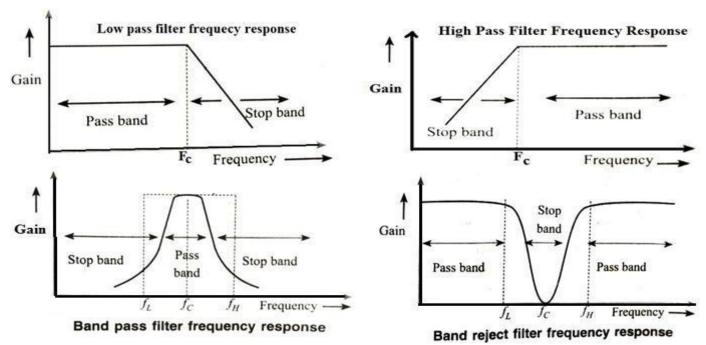

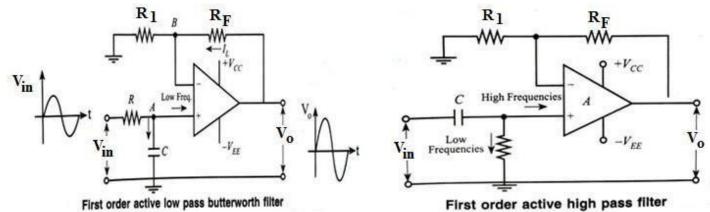

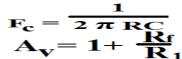

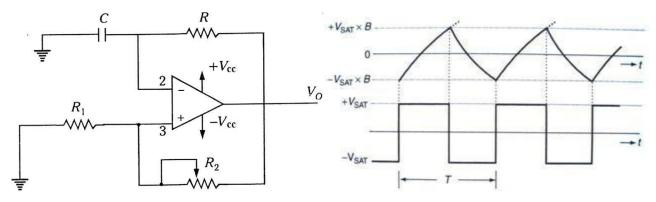

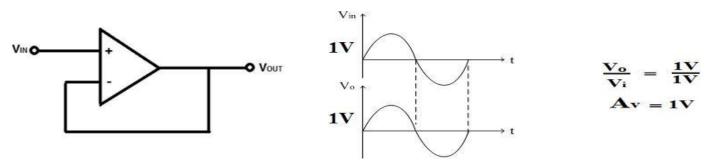

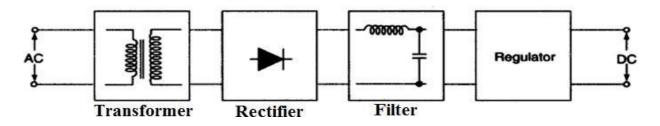

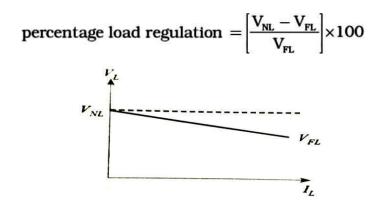

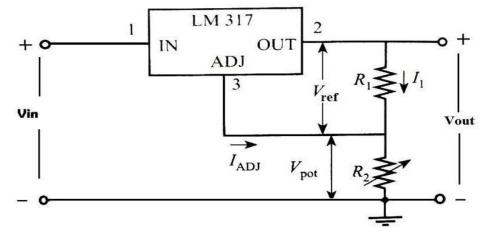

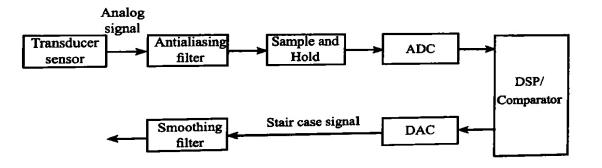

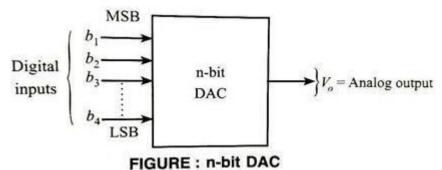

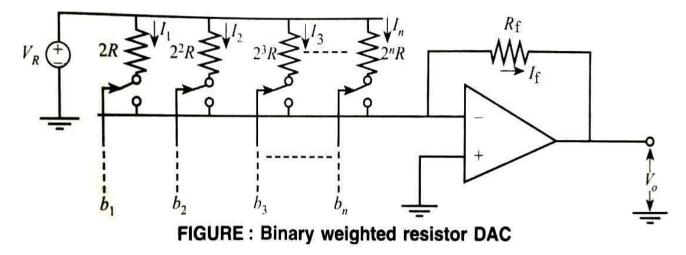

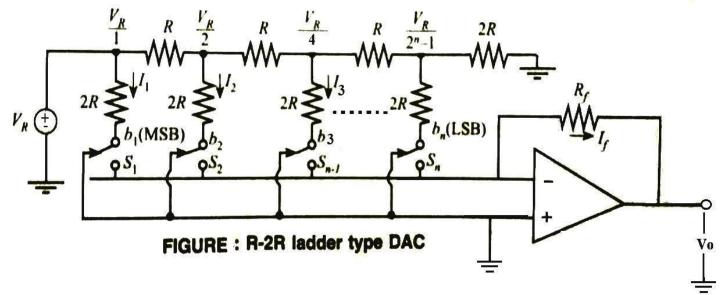

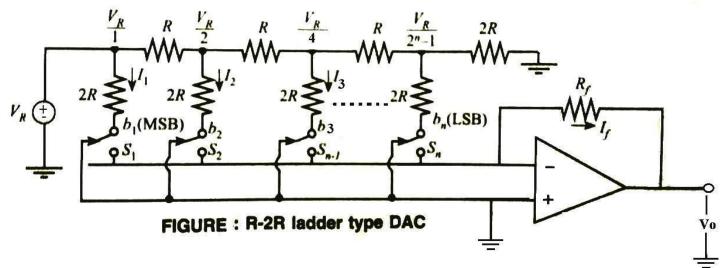

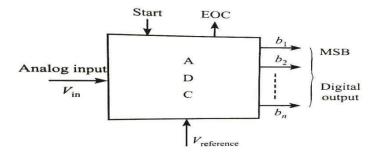

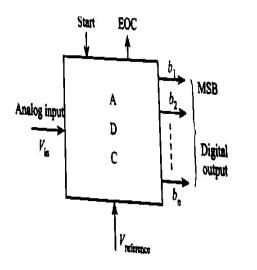

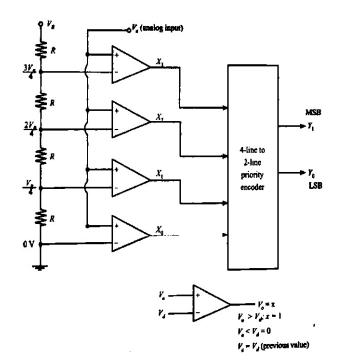

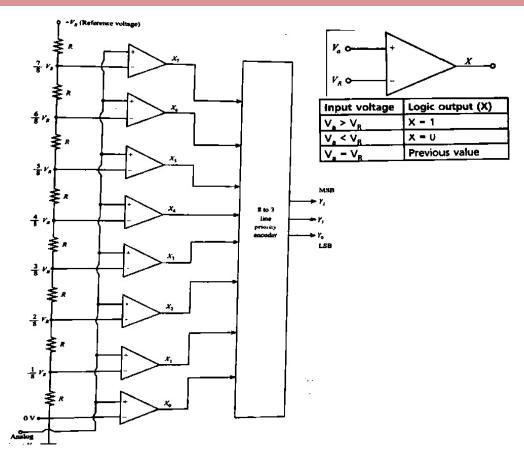

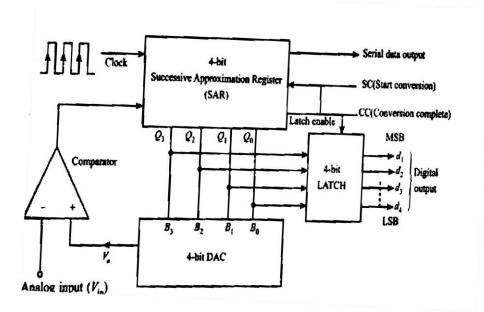

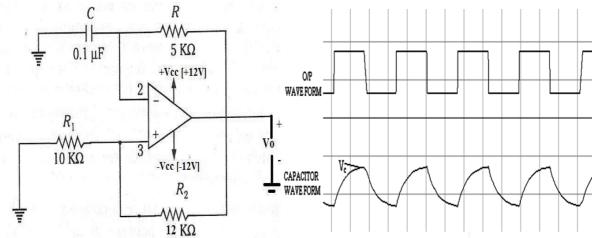

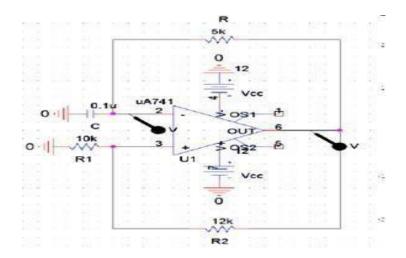

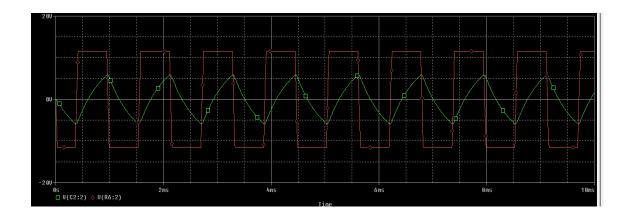

| Operational Amplifier Application C<br>Amplifier, Relaxation Oscillator, Cur<br>Power Supply Parameters, adjustabl<br><b>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | rent-to-Voltage and<br>e voltage regulator,<br><b>tions 4.2, 4.3, 4.4), (</b>                                                                                                                                                                                                                                                                                                                                    | Voltage-to-Current Conv<br>D to A and A to D conver                                                                                                                                                                                                                                                                   | verter, Regulated<br>ter.                                                                                                                                                                        |

| Amplifier, Relaxation Oscillator, Cur<br>Power Supply Parameters, adjustabl<br>Textbook 1: Part A: Chapter 4 (Sec<br>8 (Sections 8.1 and 8.5), Chapter 9<br>Laboratory Component:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rent-to-Voltage and<br>e voltage regulator,<br>tions 4.2, 4.3, 4.4), (                                                                                                                                                                                                                                                                                                                                           | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4                                                                                                                                                                                                                                        | verter, Regulated<br><sup>.</sup> ter.<br>. <b>, 7.6 to 7.11), Chapter</b>                                                                                                                       |

| Amplifier, Relaxation Oscillator, Cur<br>Power Supply Parameters, adjustabl<br>Textbook 1: Part A: Chapter 4 (Sec<br>8 (Sections 8.1 and 8.5), Chapter 9<br><i>Laboratory Component:</i><br>1. Simulate BJT CE voltage div                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rent-to-Voltage and<br>e voltage regulator,<br><b>tions 4.2, 4.3, 4.4), (</b><br>).<br>ider biased voltage a                                                                                                                                                                                                                                                                                                     | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>Amplifier using any suita                                                                                                                                                                                                           | verter, Regulated<br>rter.<br>. <b>, 7.6 to 7.11), Chapter</b><br>.ble circuit simulator.                                                                                                        |

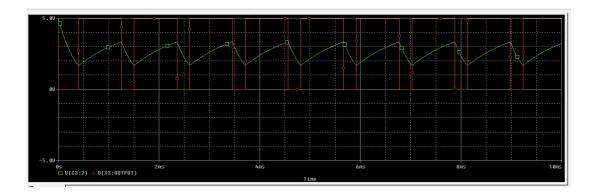

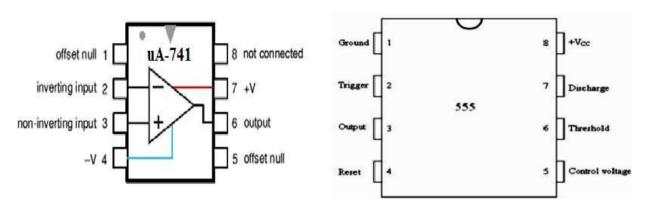

| Amplifier, Relaxation Oscillator, Cur<br>Power Supply Parameters, adjustabl<br><b>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</b><br><i>Laboratory Component:</i><br>1. Simulate BJT CE voltage div<br>2. Using ua 741 Opamp, design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rent-to-Voltage and<br>e voltage regulator,<br>tions 4.2, 4.3, 4.4), (<br>ider biased voltage a<br>n a 1 kHz Relaxation                                                                                                                                                                                                                                                                                          | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>Amplifier using any suita<br>Oscillator with 50% dut                                                                                                                                                                                | verter, Regulated<br>ter.<br><b>, 7.6 to 7.11), Chapter</b><br>ble circuit simulator.<br>y cycle                                                                                                 |

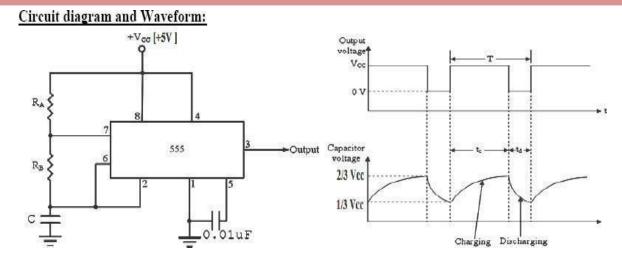

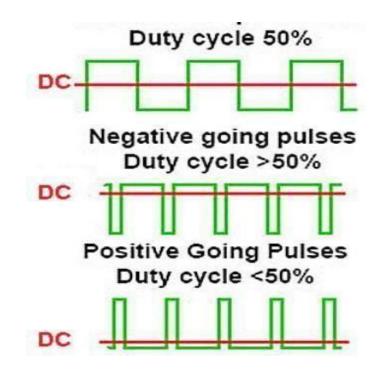

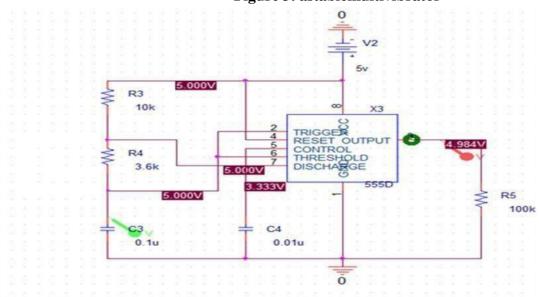

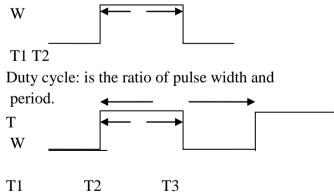

| <ul> <li>Amplifier, Relaxation Oscillator, Cur<br/>Power Supply Parameters, adjustable</li> <li>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</li> <li><i>Laboratory Component:</i> <ol> <li>Simulate BJT CE voltage div</li> <li>Using ua 741 Opamp, design</li> <li>Design an astable multivibre</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rent-to-Voltage and<br>e voltage regulator,<br>tions 4.2, 4.3, 4.4), (<br>ider biased voltage a<br>n a 1 kHz Relaxation                                                                                                                                                                                                                                                                                          | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>Amplifier using any suita<br>Oscillator with 50% dut                                                                                                                                                                                | verter, Regulated<br>ter.<br><b>, 7.6 to 7.11), Chapter</b><br>ble circuit simulator.<br>y cycle                                                                                                 |

| <ul> <li>Amplifier, Relaxation Oscillator, Cur<br/>Power Supply Parameters, adjustabl</li> <li>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</li> <li><i>Laboratory Component:</i> <ol> <li>Simulate BJT CE voltage div</li> <li>Using ua 741 Opamp, design</li> <li>Design an astable multivibration using NE 555 timer IC.</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rent-to-Voltage and<br>e voltage regulator,<br><b>tions 4.2, 4.3, 4.4), (</b><br>ider biased voltage a<br>n a 1 kHz Relaxation<br>ator circuit for three                                                                                                                                                                                                                                                         | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>amplifier using any suita<br>Oscillator with 50% dut<br>cases of duty cycle (50%                                                                                                                                                    | verter, Regulated<br>rter.<br>•, <b>7.6 to 7.11), Chapter</b><br>•ble circuit simulator.<br>y cycle<br>%, <50% and >50%)                                                                         |

| <ul> <li>Amplifier, Relaxation Oscillator, Cur<br/>Power Supply Parameters, adjustabl</li> <li>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</li> <li><i>Laboratory Component:</i> <ol> <li>Simulate BJT CE voltage div</li> <li>Using ua 741 Opamp, design</li> <li>Design an astable multivibrit</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rent-to-Voltage and<br>e voltage regulator,<br><b>tions 4.2, 4.3, 4.4), (</b><br>ider biased voltage a<br>n a 1 kHz Relaxation<br>ator circuit for three                                                                                                                                                                                                                                                         | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>amplifier using any suita<br>Oscillator with 50% dut<br>cases of duty cycle (50%                                                                                                                                                    | verter, Regulated<br>rter.<br>•, <b>7.6 to 7.11), Chapter</b><br>•ble circuit simulator.<br>y cycle<br>%, <50% and >50%)                                                                         |

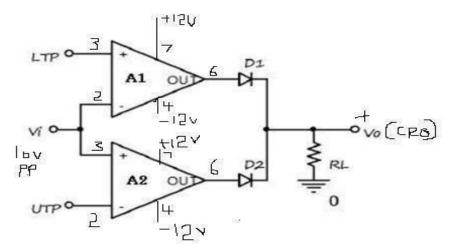

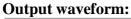

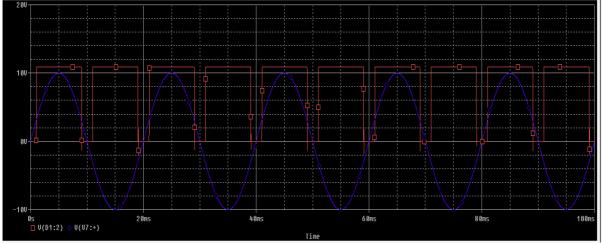

| <ul> <li>Amplifier, Relaxation Oscillator, Cur<br/>Power Supply Parameters, adjustabl</li> <li>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</li> <li><i>Laboratory Component:</i> <ol> <li>Simulate BJT CE voltage div</li> <li>Using ua 741 Opamp, design</li> <li>Design an astable multivibration using NE 555 timer IC.</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rent-to-Voltage and<br>e voltage regulator,<br>tions 4.2, 4.3, 4.4), (<br>dider biased voltage a<br>a a 1 kHz Relaxation<br>ator circuit for three                                                                                                                                                                                                                                                               | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>amplifier using any suita<br>Oscillator with 50% dut<br>cases of duty cycle (50%                                                                                                                                                    | verter, Regulated<br>ter.<br>, <b>7.6 to 7.11), Chapter</b><br>ble circuit simulator.<br>y cycle<br>%, <50% and >50%)<br>nd LTP.                                                                 |

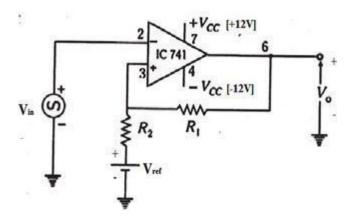

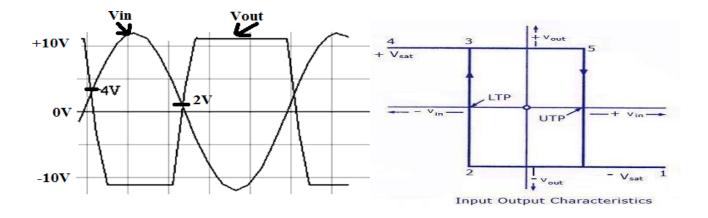

| <ul> <li>Amplifier, Relaxation Oscillator, Cur<br/>Power Supply Parameters, adjustable</li> <li>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</li> <li><i>Laboratory Component:</i> <ol> <li>Simulate BJT CE voltage div</li> <li>Using ua 741 Opamp, design</li> <li>Design an astable multivibration using NE 555 timer IC.</li> <li>Using ua 741 opamap, design</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rent-to-Voltage and<br>e voltage regulator,<br>tions 4.2, 4.3, 4.4), (<br>defined biased voltage a<br>ider biased voltage a<br>a 1 kHz Relaxation<br>ator circuit for three<br>an a window compary<br>1. Demonstra                                                                                                                                                                                               | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>Amplifier using any suita<br>Oscillator with 50% dut<br>cases of duty cycle (50%<br>ator for any given UTP a                                                                                                                        | verter, Regulated<br>rter.<br><b>, 7.6 to 7.11), Chapter</b><br>ble circuit simulator.<br>y cycle<br>%, <50% and >50%)<br>nd LTP.<br>nulation.                                                   |

| <ul> <li>Amplifier, Relaxation Oscillator, Cur<br/>Power Supply Parameters, adjustable</li> <li>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</li> <li><i>Laboratory Component:</i> <ol> <li>Simulate BJT CE voltage div</li> <li>Using ua 741 Opamp, design</li> <li>Design an astable multivibration using NE 555 timer IC.</li> <li>Using ua 741 opamap, design</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rent-to-Voltage and<br>e voltage regulator,<br>tions 4.2, 4.3, 4.4), (<br>dider biased voltage a<br>n a 1 kHz Relaxation<br>ator circuit for three<br>n a window compara<br>1. Demonstra<br>2. Project wor                                                                                                                                                                                                       | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>Amplifier using any suita<br>Oscillator with 50% dut<br>cases of duty cycle (50%<br>ator for any given UTP a<br>tion of circuits using sin                                                                                          | verter, Regulated<br>rter.<br><b>, 7.6 to 7.11), Chapter</b><br>ble circuit simulator.<br>y cycle<br>%, <50% and >50%)<br><u>nd LTP.</u><br>pulation.<br>power supply and                        |

| <ul> <li>Amplifier, Relaxation Oscillator, Cur<br/>Power Supply Parameters, adjustable</li> <li>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</li> <li><i>Laboratory Component:</i> <ol> <li>Simulate BJT CE voltage div</li> <li>Using ua 741 Opamp, design</li> <li>Design an astable multivibration using NE 555 timer IC.</li> <li>Using ua 741 opamap, design</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rent-to-Voltage and<br>e voltage regulator,<br>tions 4.2, 4.3, 4.4), (<br>dider biased voltage a<br>n a 1 kHz Relaxation<br>ator circuit for three<br>n a window compar-<br>1. Demonstra<br>2. Project won<br>function ge                                                                                                                                                                                        | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>amplifier using any suita<br>Oscillator with 50% dut<br>cases of duty cycle (50%<br>ator for any given UTP a<br>tion of circuits using sin<br>rk: Design a integrated p                                                             | verter, Regulated<br>ter.<br>, <b>7.6 to 7.11), Chapter</b><br>ble circuit simulator.<br>y cycle<br>%, <50% and >50%)<br><u>nd LTP.</u><br>nulation.<br>oower supply and<br>dio frequency. Sine, |

| <ul> <li>Amplifier, Relaxation Oscillator, Cur<br/>Power Supply Parameters, adjustable</li> <li>Textbook 1: Part A: Chapter 4 (Sec<br/>8 (Sections 8.1 and 8.5), Chapter 9</li> <li><i>Laboratory Component:</i> <ol> <li>Simulate BJT CE voltage div</li> <li>Using ua 741 Opamp, design</li> <li>Design an astable multivibration using NE 555 timer IC.</li> <li>Using ua 741 opamap, design</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rent-to-Voltage and<br>e voltage regulator,<br>tions 4.2, 4.3, 4.4), (<br>dider biased voltage a<br>in a 1 kHz Relaxation<br>ator circuit for three<br>n a window compary<br>1. Demonstra<br>2. Project wor<br>function ge<br>square and                                                                                                                                                                         | Voltage-to-Current Conv<br>D to A and A to D conver<br>Chapter 7 (Sections 7.4<br>Amplifier using any suita<br>Oscillator with 50% dut<br>cases of duty cycle (50%<br>ator for any given UTP a<br>tion of circuits using sim<br>rk: Design a integrated p<br>nerator operating at au                                  | verter, Regulated<br>ter.<br>, <b>7.6 to 7.11), Chapter</b><br>ble circuit simulator.<br>y cycle<br>%, <50% and >50%)<br><u>nd LTP.</u><br>nulation.<br>ower supply and<br>dio frequency. Sine,  |

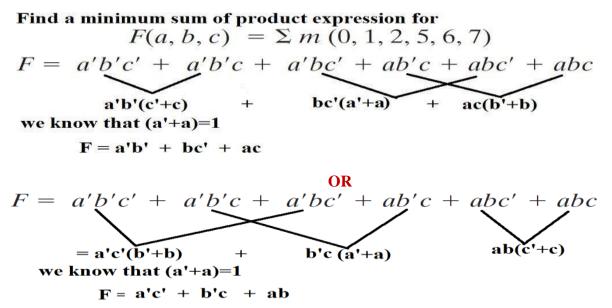

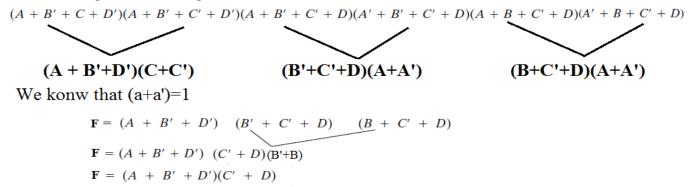

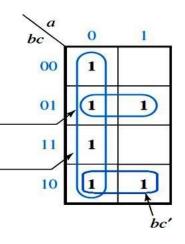

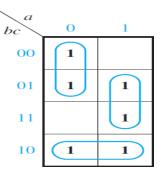

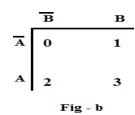

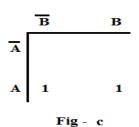

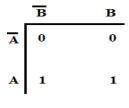

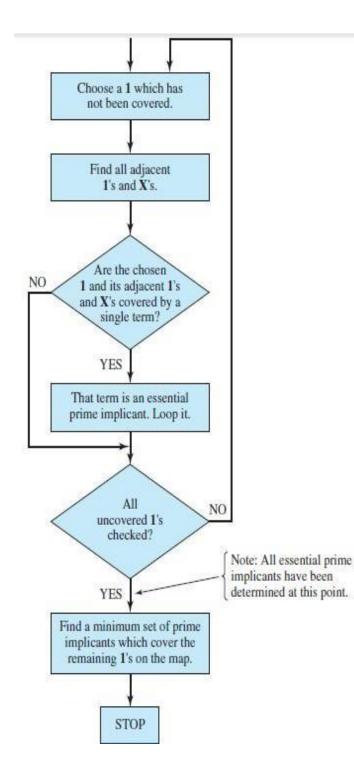

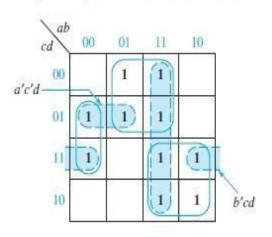

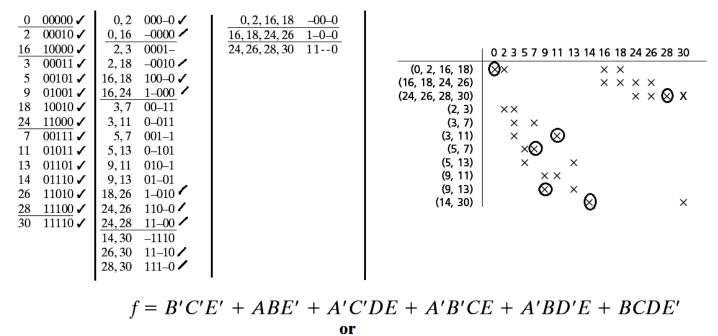

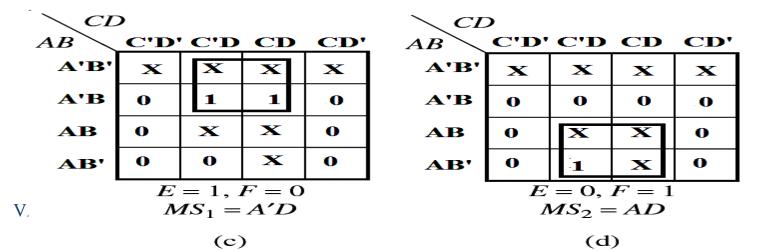

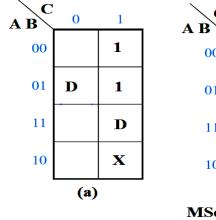

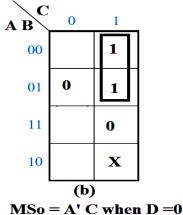

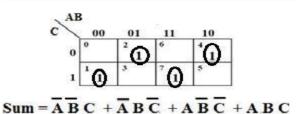

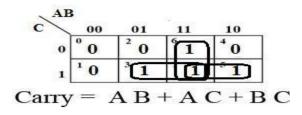

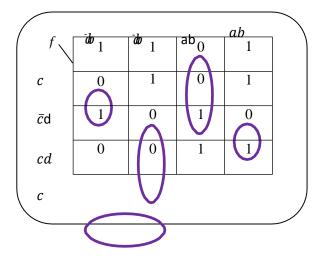

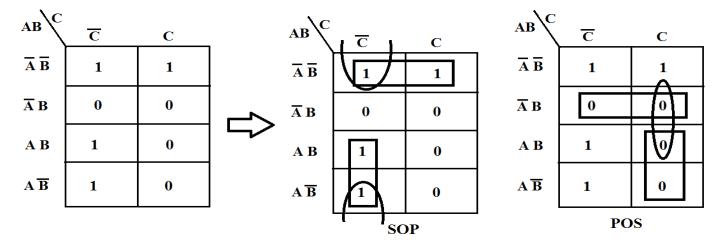

Karnaugh maps: minimum forms of switching functions, two and three variable Karnaugh maps, four variable Karnaugh maps, determination of minimum expressions using essential prime implicants, Quine-McClusky Method: determination of prime implicants, the prime implicant chart, Petricks method, simplification of incompletely specified functions, simplification using map-entered variables

# Textbook 1: Part B: Chapter 5 (Sections 5.1 to 5.4) Chapter 6 (Sections 6.1 to 6.5)

#### Laboratory Component:

1. Given a 4-variable logic expression, simplify it using appropriate technique and inplement the same using basic gates.

| Teaching-Learning Process   | 1. | Chalk and Board for numerical |  |  |  |

|-----------------------------|----|-------------------------------|--|--|--|

| 2. Laboratory Demonstration |    |                               |  |  |  |

|                             |    | Module-3                      |  |  |  |

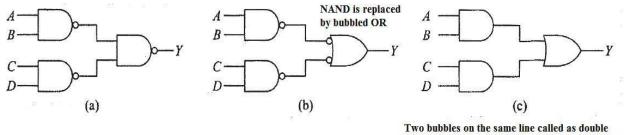

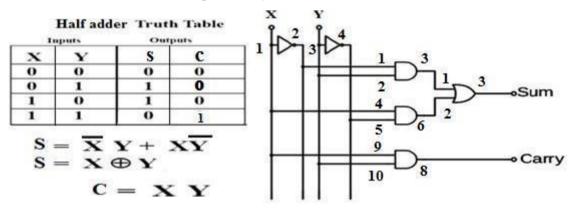

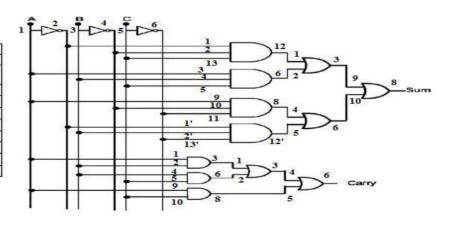

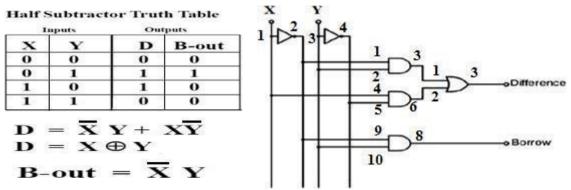

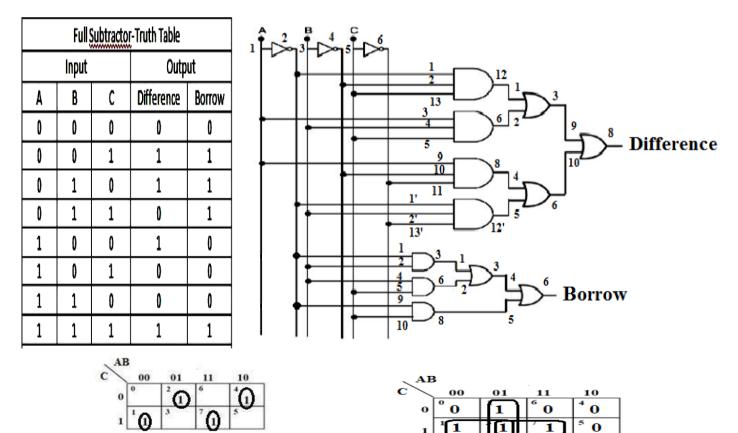

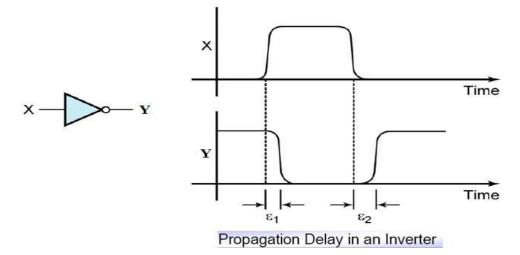

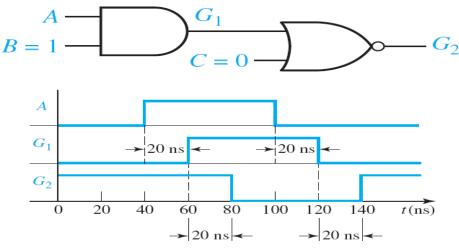

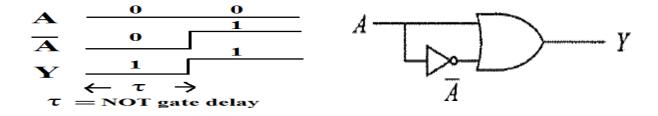

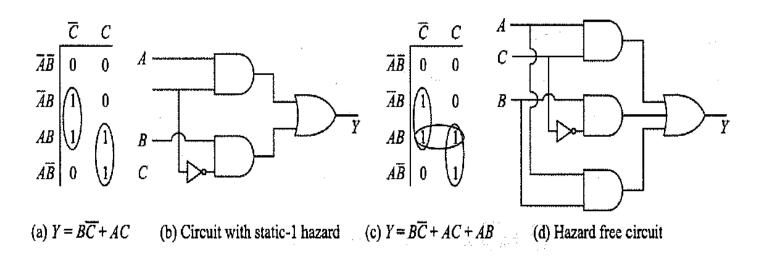

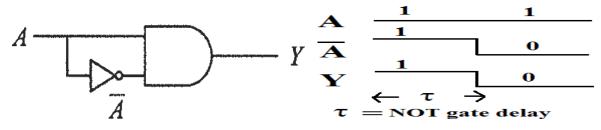

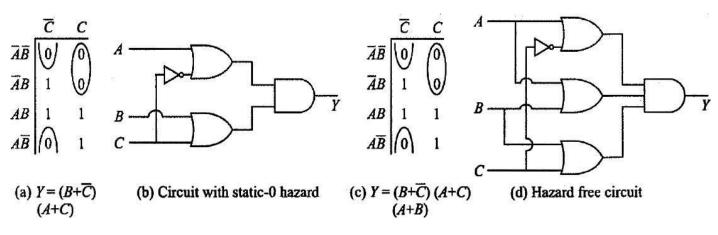

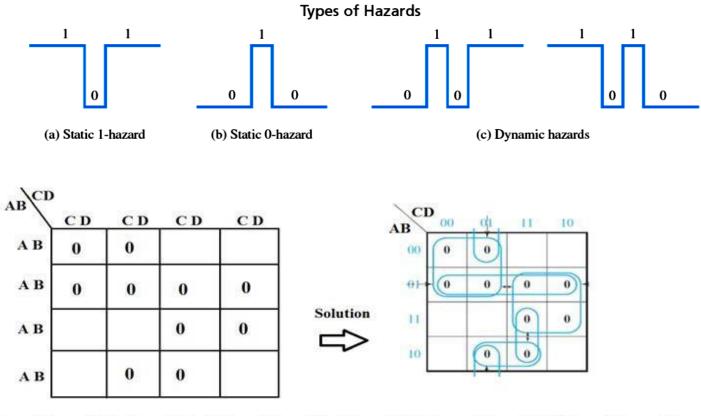

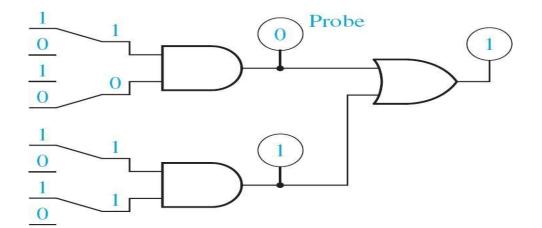

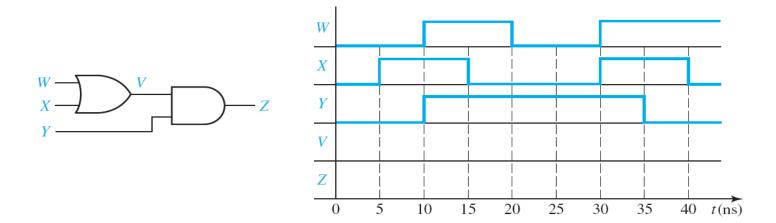

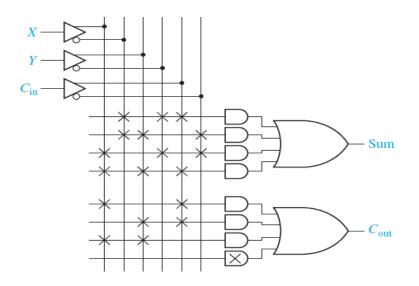

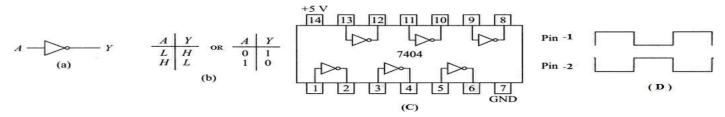

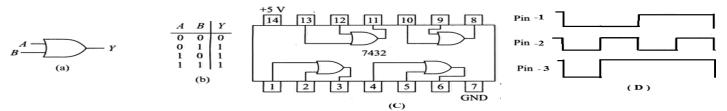

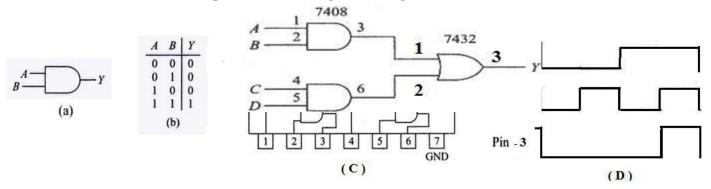

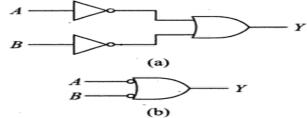

Combinational circuit design and simulation using gates: Review of Combinational circuit design, design of circuits with limited Gate Fan-in, Gate delays and Timing diagrams, Hazards in combinational Logic, simulation and testing of logic circuits

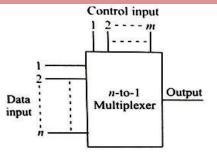

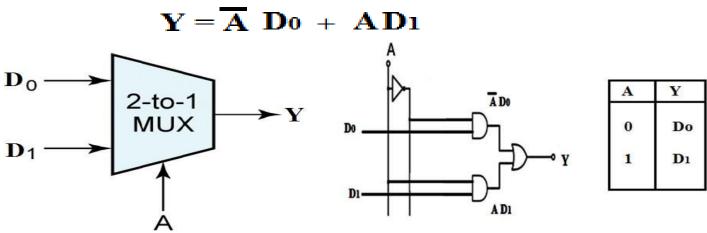

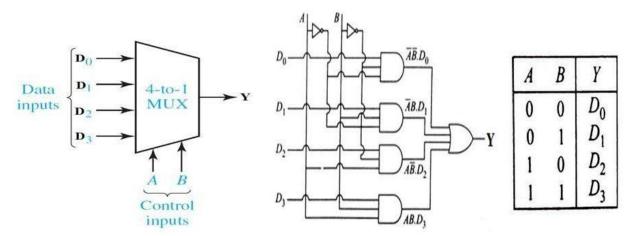

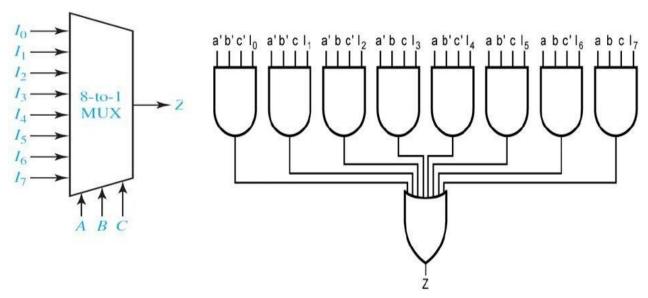

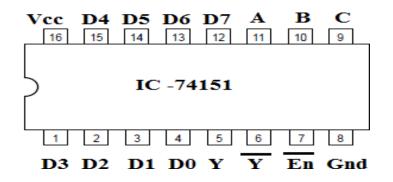

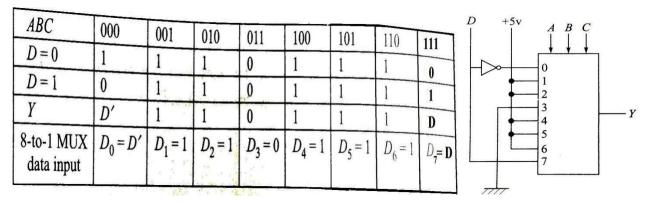

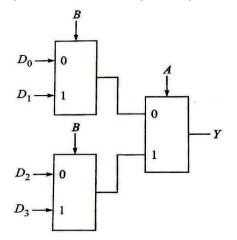

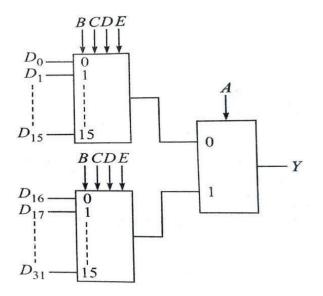

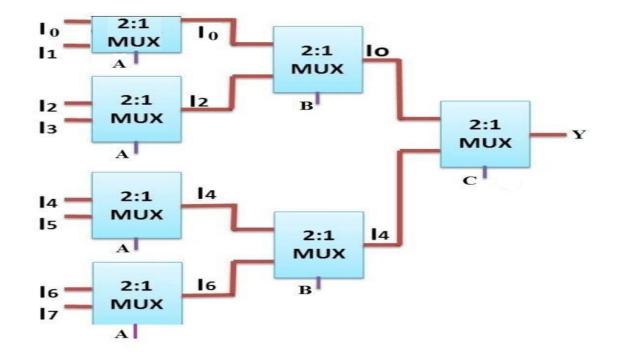

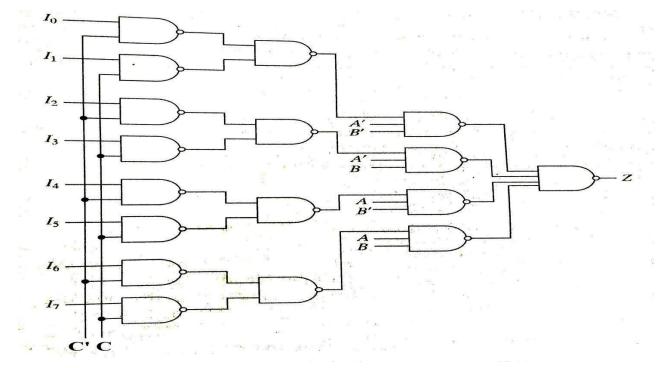

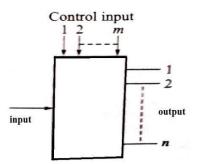

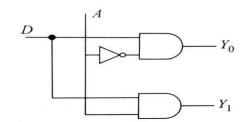

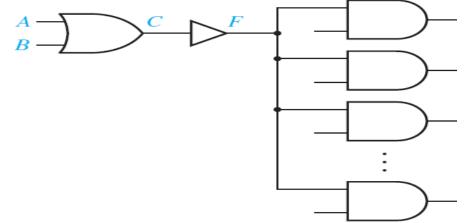

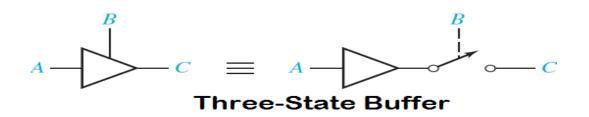

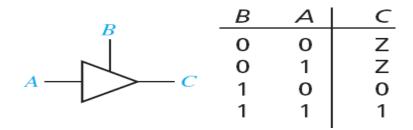

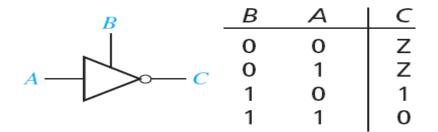

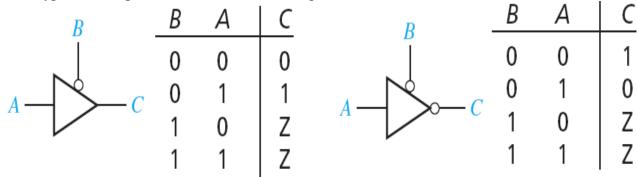

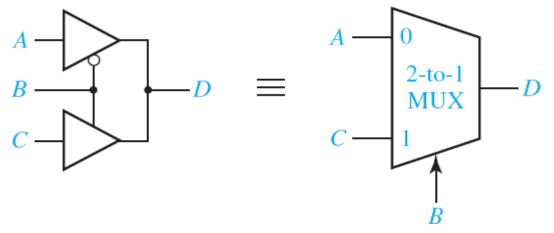

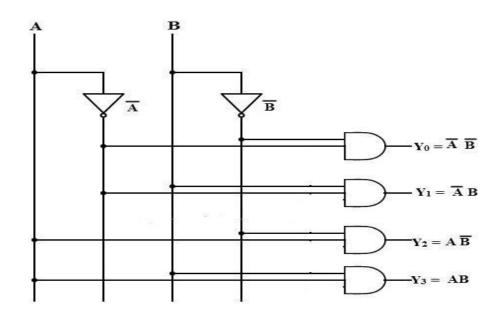

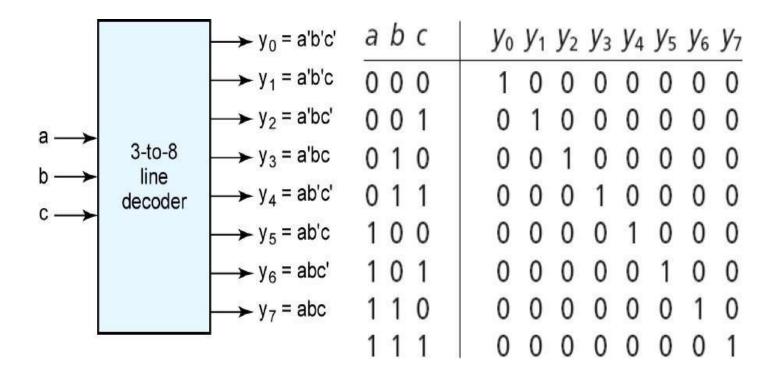

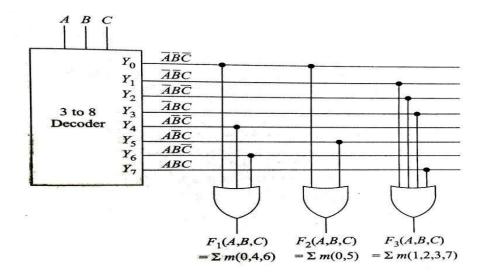

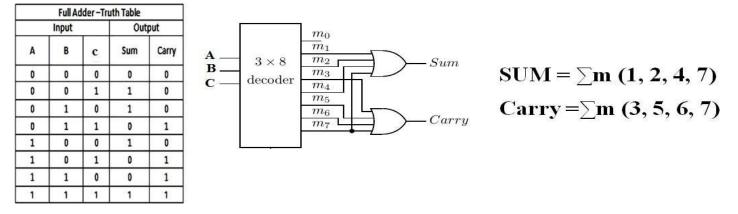

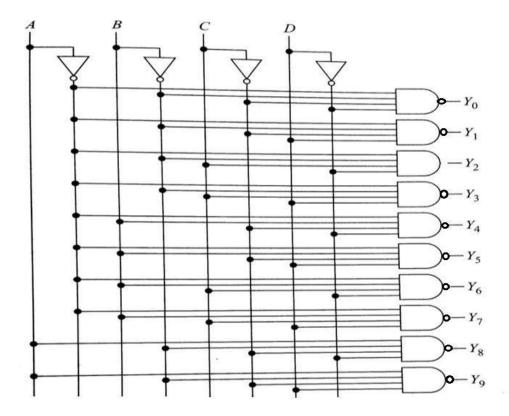

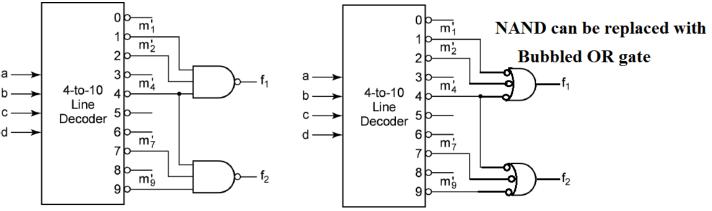

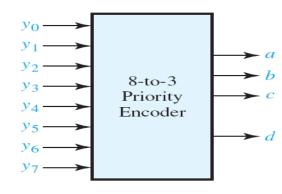

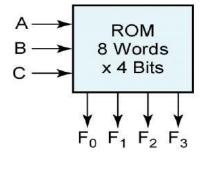

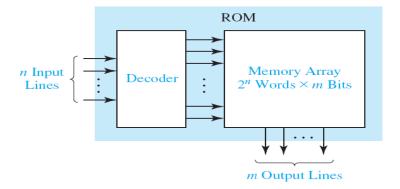

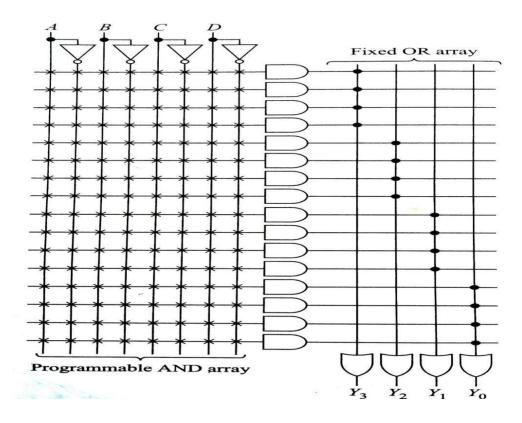

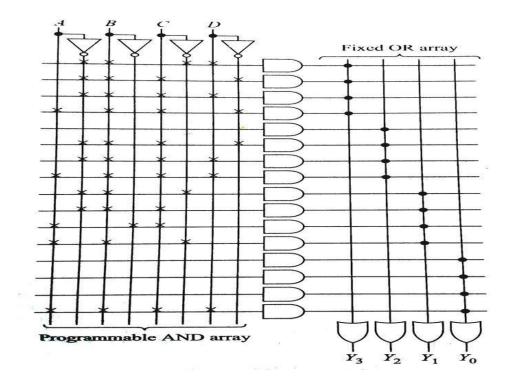

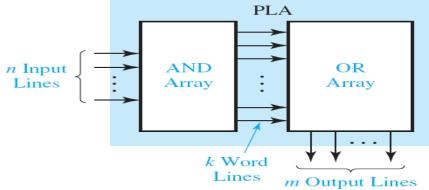

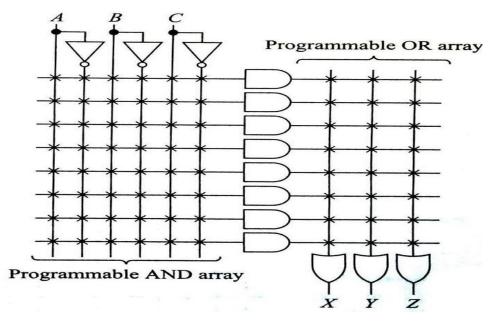

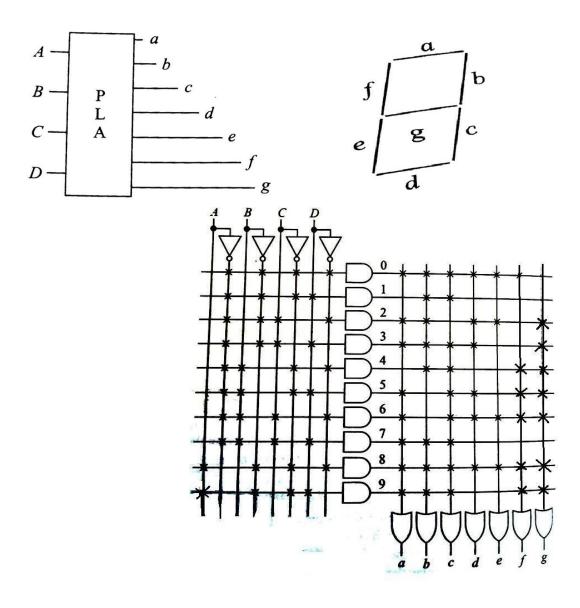

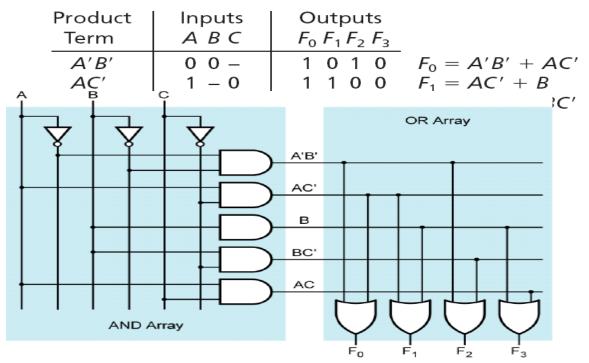

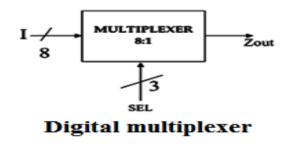

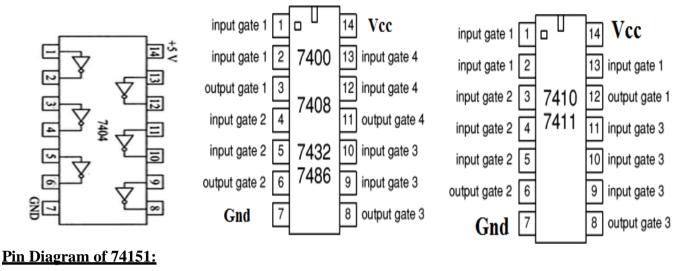

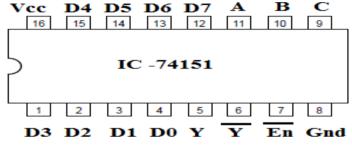

Multiplexers, Decoders and Programmable Logic Devices: Multiplexers, three state buffers, decoders and encoders, Programmable Logic devices.

#### Textbook 1: Part B: Chapter 8, Chapter 9 (Sections 9.1 to 9.6)

#### Laboratory Component:

1. Given a 4-variable logic expression, simplify it using appropriate technique and realize the simplified logic expression using 8:1 multiplexer IC.

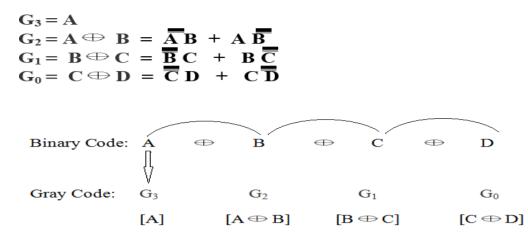

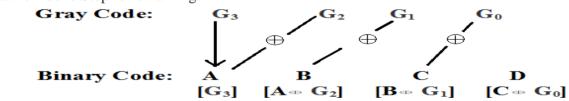

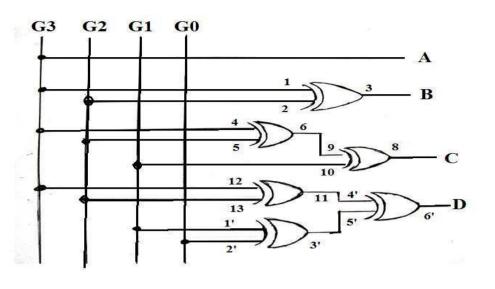

| 2. Design and implement code                                                                                                                                               | e converter I) Binary to Gray (II) Gray to Binary Code   |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|

| Teaching-Learning Process       1. Demonstration using simulator         2. Case study: Applications of Programmable Logic device         3. Chalk and Board for numerical |                                                          |  |  |  |  |  |  |

|                                                                                                                                                                            | 2. Case study: Applications of Programmable Logic device |  |  |  |  |  |  |

|                                                                                                                                                                            | 3. Chalk and Board for numerical                         |  |  |  |  |  |  |

| Module-4                                                                                                                                                                   |                                                          |  |  |  |  |  |  |

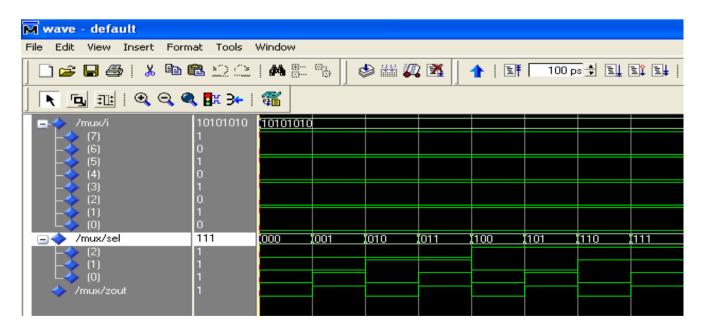

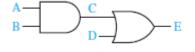

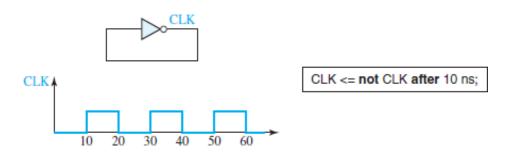

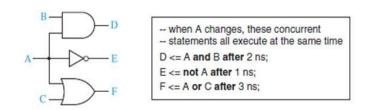

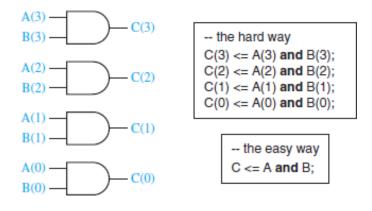

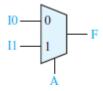

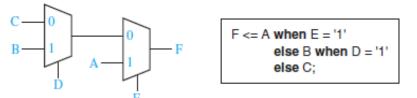

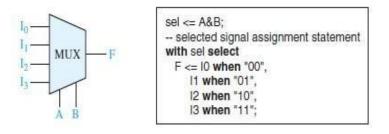

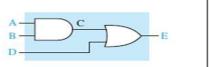

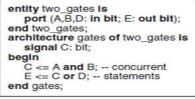

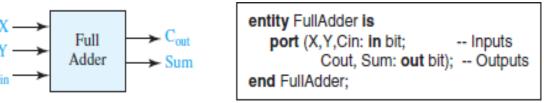

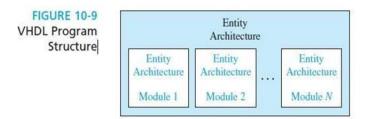

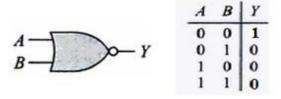

Introduction to VHDL: VHDL description of combinational circuits, VHDL Models for multiplexers, VHDL Modules.

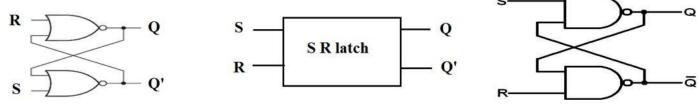

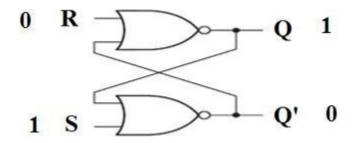

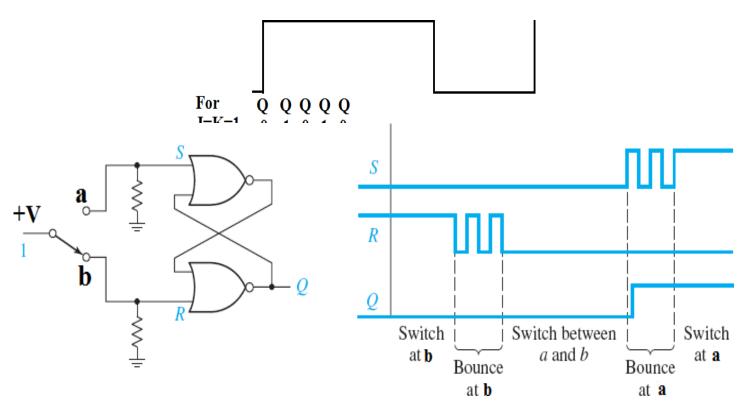

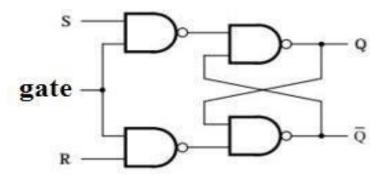

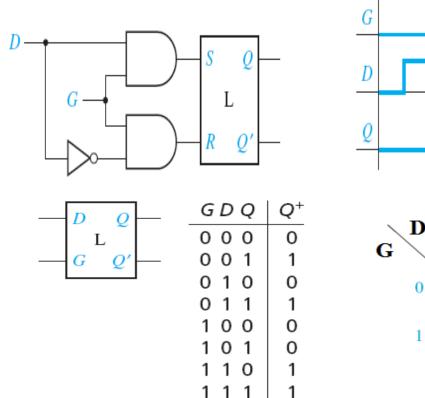

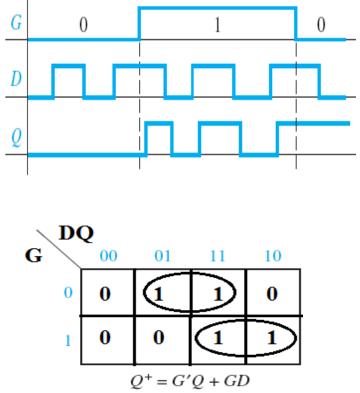

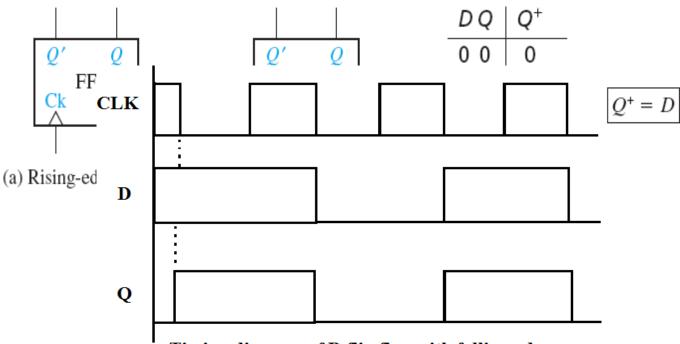

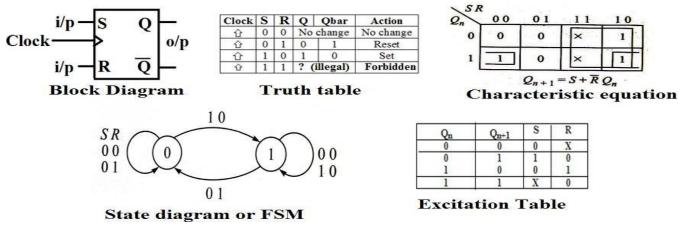

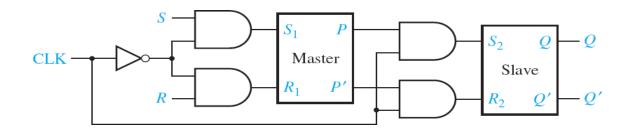

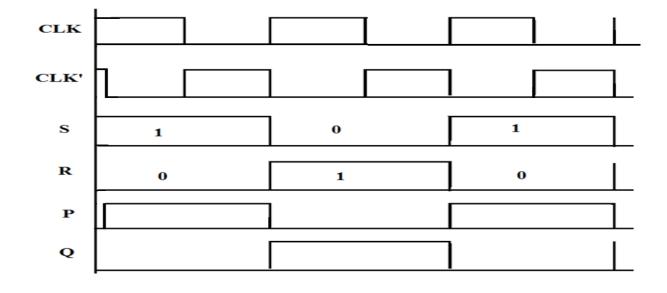

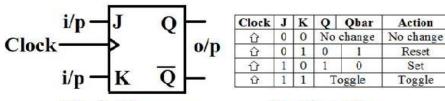

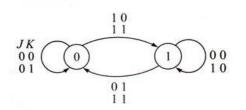

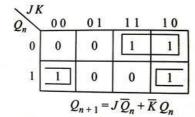

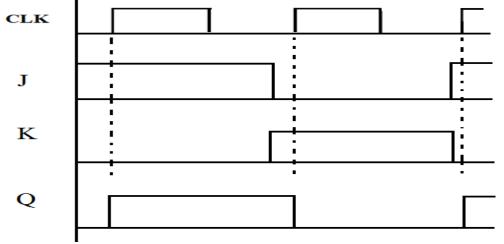

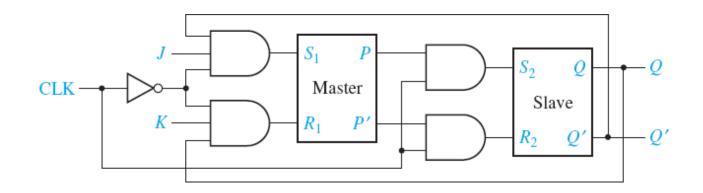

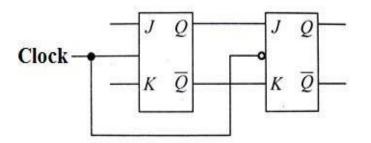

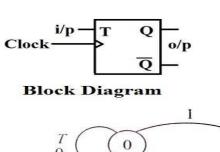

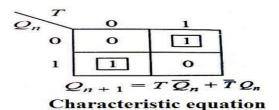

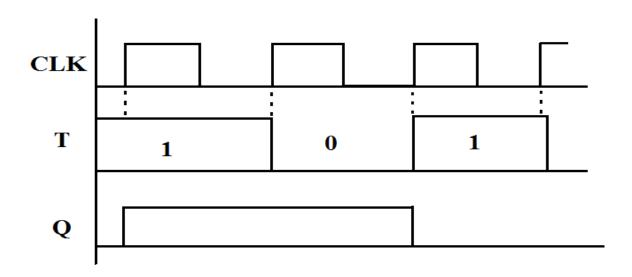

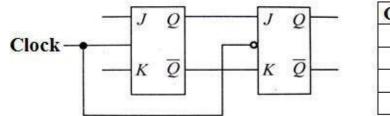

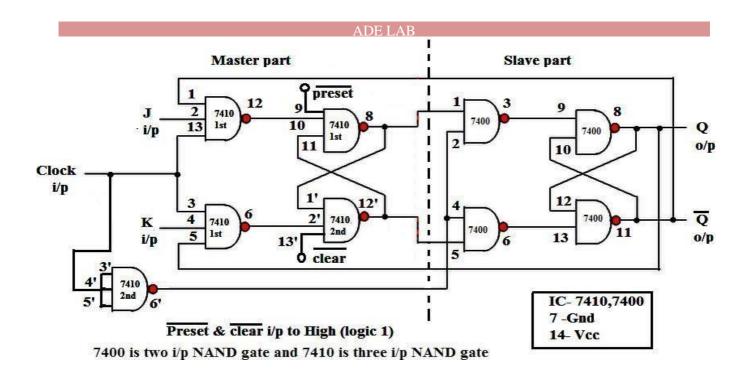

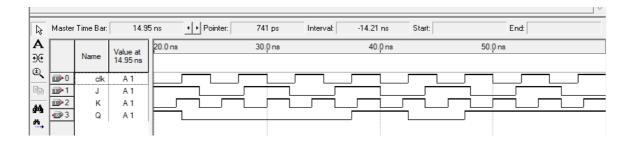

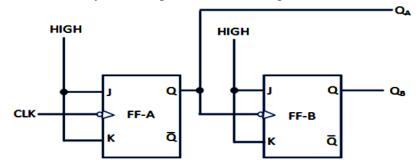

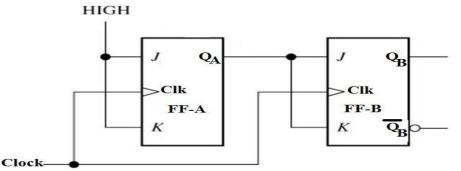

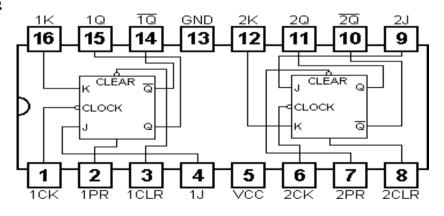

Latches and Flip-Flops: Set Reset Latch, Gated Latches, Edge-Triggered D Flip Flop 3, SR Flip Flop, J K Flip Flop, T Flip Flop.

#### Textbook 1: Part B: Chapter 10(Sections 10.1 to 10.3), Chapter 11 (Sections 11.1 to 11.7)

#### Laboratory Component:

- 1. Given a 4-variable logic expression, simplify it using appropriate technique and simulate the same in HDL simulator

- 2. Realize a J-K Master / Slave Flip-Flop using NAND gates and verify its truth table. And implement the same in HDL.

| Teaching-Learning Process                                                                                | 1. | Demonstration using simulator                 |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|----|-----------------------------------------------|--|--|--|--|--|--|

|                                                                                                          | 2. | Case study: Arithmetic and Logic unit in VHDL |  |  |  |  |  |  |

| 3. Chalk and Board for numerical                                                                         |    |                                               |  |  |  |  |  |  |

| Module-5                                                                                                 |    |                                               |  |  |  |  |  |  |

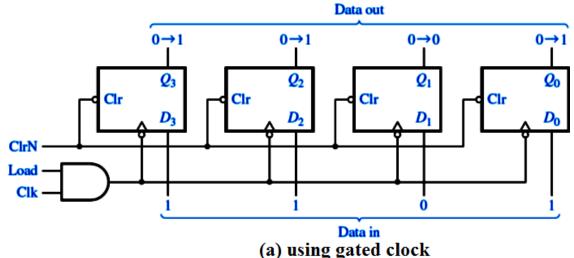

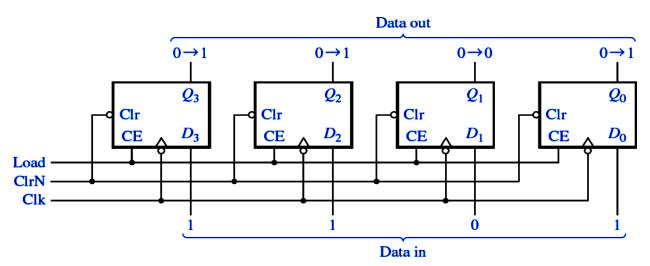

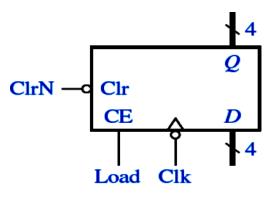

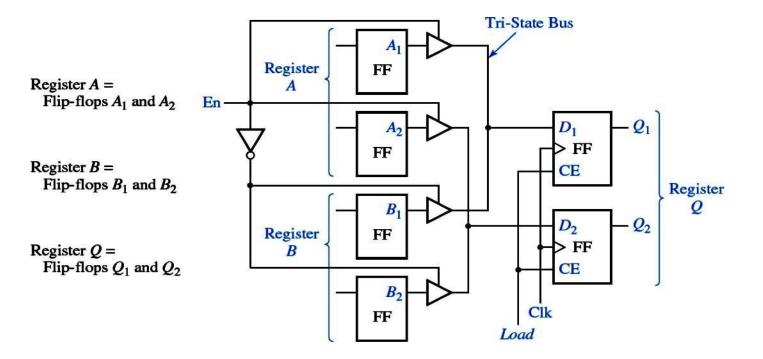

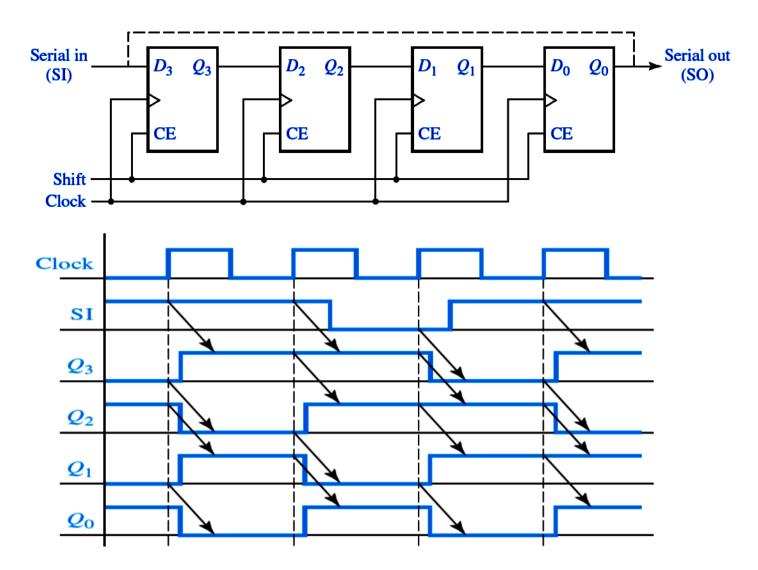

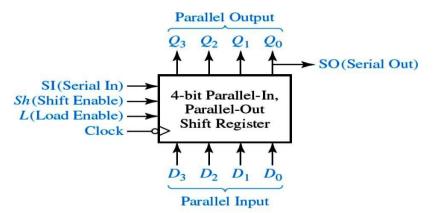

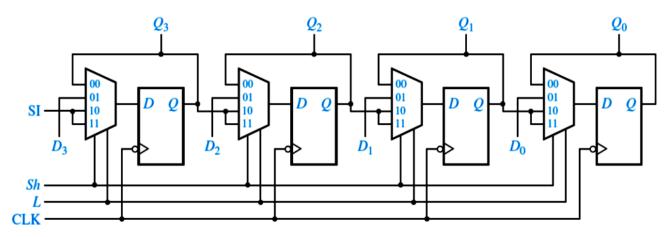

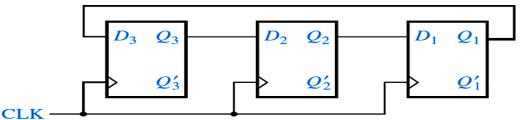

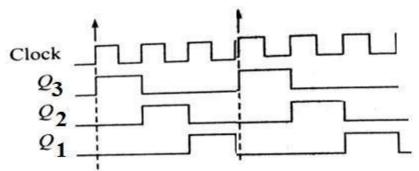

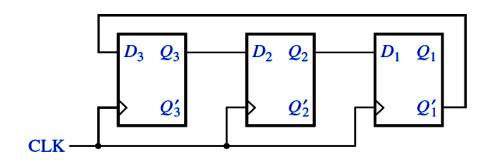

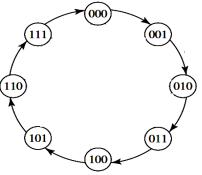

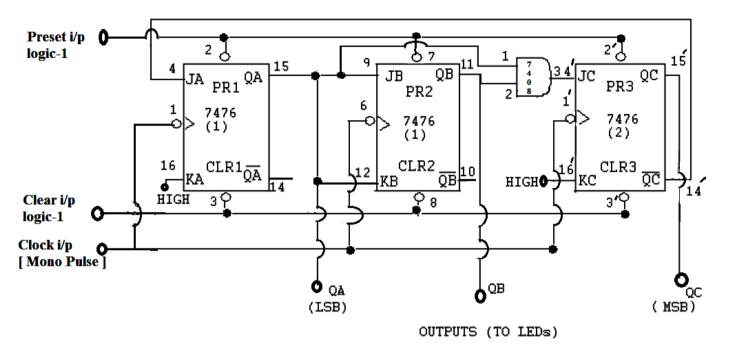

| Registers and Counters: Registers and Register Transfers, Parallel Adder with accumulator, shift         |    |                                               |  |  |  |  |  |  |

| registers, design of Binary counters, counters for other sequences, counter design using SR and J K Flip |    |                                               |  |  |  |  |  |  |

| Flops.                                                                                                   |    |                                               |  |  |  |  |  |  |

### Textbook 1: Part B: Chapter 12 (Sections 12.1 to 12.5)

#### Laboratory Component:

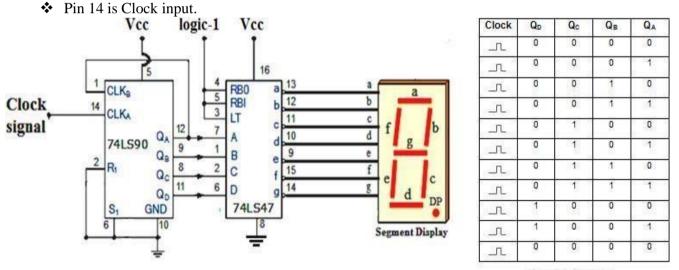

- 1. Design and implement a mod-n (n<8) synchronous up counter using J-K Flip-Flop ICs and demonstrate its working.

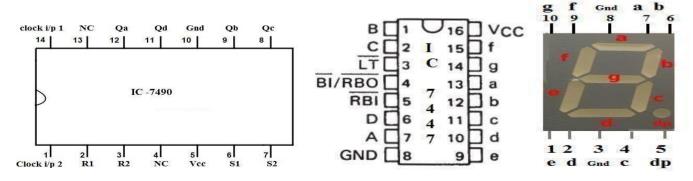

- Design and implement an asynchronous counter using decade counter IC to count up from 0 to n (n<=9) and demonstrate on 7-segment display (using IC-7447)</li>

| Teaching-Learning Process        | 1. | Demonstration using simulator                         |

|----------------------------------|----|-------------------------------------------------------|

|                                  | 2. | Project Work: Designing any counter, use LED / Seven- |

|                                  |    | segment display to display the output                 |

|                                  | 3. | Chalk and Board for numerical                         |

| Course outcome (Course Skill Set | .) |                                                       |

At the end of the course the student will be able to:

- CO 1. Design and analyze application of analog circuits using photo devices, timer IC, power supply and regulator IC and op-amp.

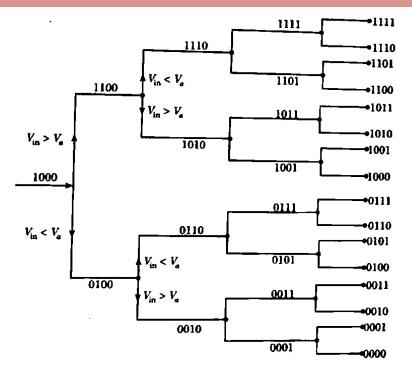

- CO 2. Explain the basic principles of A/D and D/A conversion circuits and develop the same.

- CO 3. Simplify digital circuits using Karnaugh Map, and Quine-McClusky Methods

- CO 4. Explain Gates and flip flops and make us in designing different data processing circuits, registers and counters and compare the types.

- CO 5. Develop simple HDL programs

# Assessment Details (both CIE and SEE)

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks). A student shall be deemed to have satisfied the academic requirements and earned the credits allotted to each subject/ course if the student secures not less than 35% (18 Marks out of 50) in the semester-end examination (SEE), and a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together

#### **Continuous Internal Evaluation:**

Three Unit Tests each of **20 Marks (duration 01 hour**)

- 1. First test at the end of  $5^{th}$  week of the semester

- 2. Second test at the end of the  $10^{th}$  week of the semester

- **3.** Third test at the end of the 15<sup>th</sup> week of the semester

Two assignments each of **10 Marks**

- 4. First assignment at the end of 4<sup>th</sup> week of the semester

- 5. Second assignment at the end of 9<sup>th</sup> week of the semester

Practical Sessions need to be assessed by appropriate rubrics and viva-voce method. This will contribute to **20 marks**.

- Rubrics for each Experiment taken average for all Lab components 15 Marks.

- Viva-Voce- 5 Marks (more emphasized on demonstration topics)

The sum of three tests, two assignments, and practical sessions will be out of 100 marks and will be **scaled down to 50 marks**

(to have a less stressed CIE, the portion of the syllabus should not be common /repeated for any of the methods of the CIE. Each method of CIE should have a different syllabus portion of the course). **CIE methods /question paper has to be designed to attain the different levels of Bloom's taxonomy as per the outcome defined for the course.**

Semester End Examination:

Theory SEE will be conducted by University as per the scheduled timetable, with common question papers for the subject (**duration 03 hours**)

- 1. The question paper will have ten questions. Each question is set for 20 marks. Marks scored shall be proportionally reduced to 50 marks

- 2. There will be 2 questions from each module. Each of the two questions under a module (with a maximum of 3 sub-questions), **should have a mix of topics** under that module.

The students have to answer 5 full questions, selecting one full question from each module

# Suggested Learning Resources:

#### Textbooks

1. Charles H Roth and Larry L Kinney and Raghunandan G H Analog and Digital Electronics, Cengage Learning, 2019

# **Reference Books**

- 1. Anil K Maini, Varsha Agarwal, Electronic Devices and Circuits, Wiley, 2012.

- 2. Donald P Leach, Albert Paul Malvino & Goutam Saha, Digital Principles and Applications, 8th Edition, Tata McGraw Hill, 2015.

- 3. M. Morris Mani, Digital Design, 4th Edition, Pearson Prentice Hall, 2008.

- 4. David A. Bell, Electronic Devices and Circuits, 5th Edition, Oxford University Press, 2008

# Weblinks and Video Lectures (e-Resources):

- 1. Analog Electronic Circuits: https://nptel.ac.in/courses/108/102/108102112/

- 2. Digital Electronic Circuits: https://nptel.ac.in/courses/108/105/108105132/

- 3. Analog Electronics Lab: http://vlabs.iitkgp.ac.in/be/

- 4. Digital Electronics Lab: http://vlabs.iitkgp.ac.in/dec

# Activity Based Learning (Suggested Activities in Class)/ Practical Based learning

1. Real world problem solving - applying the design concepts of oscillator, amplifier, switch, Digital circuits using Opamps, 555 timer, transistor, Digital ICs and design a application like tone generator, temperature sensor, digital clock, dancing lights etc.

# **MODULE -1**

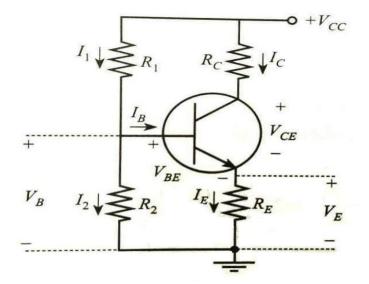

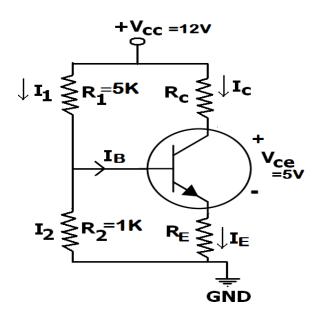

### **BJT BIASING**

- Biasing is a process of connecting DC voltage source to the junction of transistor to make it to operate in the desired region.

- ♦ Biasing eliminates the need for separate DC source in the emitter and collector circuit.

### **Types of Biasing:**

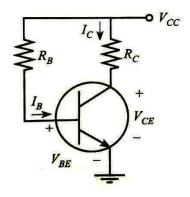

#### (i) Base Bias or Fixed Bias

- ◆ The resistance R<sub>B</sub> is connected between V<sub>CC</sub> and base of transistor to establish I<sub>B</sub>.

- ✤ Because V<sub>CC</sub> and R<sub>B</sub> are fixed, I<sub>B</sub> remains fixed hence it is called as fixed bias.

## By applying KVL to the base of circuit we get

$V_{BE}$  is 0.7V for silicon and 0.3v for germanium transistor.

$$V_{cc} - I_B R_B - V_{BE} = 0$$

$$I_B R_B + V_{BE} = V_{CC}$$

$$\Rightarrow \qquad I_B = \frac{V_{CC} - V_{BE}}{R_B}$$

$$I_C = \beta I_B$$

$$V_{CC} = V_{CC} + I_C R_C$$

$$V_{CE} = V_{CC} - I_C R_C$$

The collector current is calculated as By applying KVL to the collector circuit we get

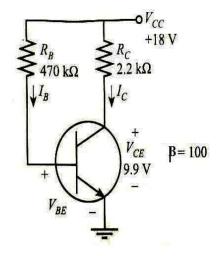

**Prob-1**) The base bias circuit shown below determine the values of  $I_C$ ,  $I_B$  and  $V_{CE}$ . **Soln:**

Given:  $R_B = 470 \text{ k}\Omega$ ,  $R_C = 2.2 \text{ k}\Omega$ ,  $V_{CC} = 18 \text{ V}$   $I_B = \frac{V_{CC} - V_{BE}}{R_B} = \frac{18 \text{ V} - 0.7 \text{ V}}{470 \text{ k}\Omega} = 36.8 \text{ }\mu\text{A}$   $I_C = \beta I_B = 100 \times 36.8 \text{ }\mu\text{A} = 3.68 \text{ }\text{m}\text{A}$  $V_{CE} = V_{CE} - I_C R_C = 18 \text{ V} - (3.68 \text{ }\text{m}\text{A} \times 2.2 \text{ }\text{k}\Omega) = 9.9 \text{ V}$

**Prob-2**) For the above base bias circuit, calculate the maximum and minimum level I<sub>C</sub> and V<sub>CE</sub>. Given  $\beta$  =200 and  $\beta$ =50.

#### Soln: $I_B = 36.8 \mu A$

For  $\beta$  =200, I<sub>C</sub>=7.36mA and V<sub>CE</sub>=1.8V and For  $\beta$  =50, I<sub>C</sub>=1.84mA and V<sub>CE</sub>=13.85V

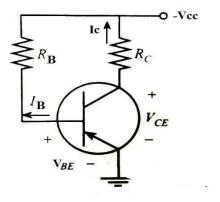

#### **Base Bias using PNP transistor:**

The explanation for base biasof PNP is similar to the NPN but the difference is polarities of voltage and currents.

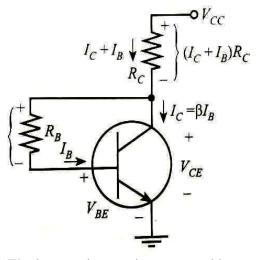

#### (ii) Collector to Base Bias:

The base resistance is connected between the transistor collector and base terminal Apply KVL to the outer loop (between collector and emitter)

$$-V_{CE} - R_{C} (I_{C}+I_{B}) + V_{CC} = 0$$

$$V_{CC} = R_{C} (I_{B} + I_{C}) + V_{CE}$$

$$V_{CE} = V_{CC} - R_{C} (I_{B} + I_{C})$$

Also KVL to the loop  $V_{CE}$ ,  $I_{B}R_{B}$  and  $V_{BE}$

$$-V_{BE} - I_{B}R_{B} + V_{CE} = 0$$

$$V_{CE} = I_{B}R_{B} + V_{BE}$$

on equating above equations leads to

$$I_{B} (R_{C} + R_{B}) + I_{C} R_{C} = V_{CC} - V_{BE}$$